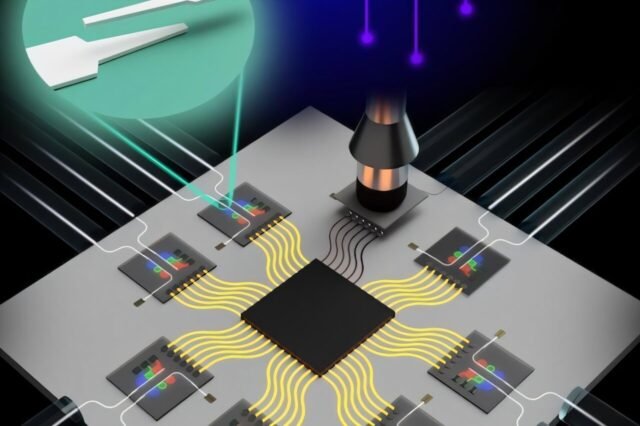

El dispositivo MIT en la llamada verde podría ser clave para una comunicación de datos más rápida y eficiente en energía. Resuelve un problema importante asociado con el embalaje de un chip eléctrico (negro, centro) con chips fotónicos (los ocho cuadrados circundantes). Esta imagen también muestra una herramienta automatizada que coloca el chip fotónico final en posición. Crédito: Drew Weninger, MIT.

El futuro de la computación y las comunicaciones digitales involucrará tanto a la electrónica (datos de manipulación con electricidad y fotónica, o hacer lo mismo con la luz. Juntos, los dos podrían permitir exponencialmente más tráfico de datos en todo el mundo en un proceso que también es más eficiente en energía.

“La conclusión es que la integración de la fotónica con la electrónica en el mismo paquete es el transistor para el siglo XXI. Si no podemos entender cómo hacerlo, entonces no vamos a poder escalar hacia adelante”, dice Lionel Kimerling, el Profesor de Ciencia e Ingeniería de Materiales de Thomas Lord en MIT y director del Centro de microfotonics MIT.

Ingrese Futur-IC, un nuevo equipo de investigación con sede en el MIT. “Nuestro objetivo es construir una cadena de valor de la industria de microchip que sea eficiente en recursos”, dice Anu Agarwal, jefe de Futur-IC y científico principal de investigación del Laboratorio de Investigación de Materiales (MRL).

Ahora, los investigadores de Futur-IC, incluidos Agarwal y Kimerling, han desarrollado una nueva forma de empaquetar chips fotónicos con sus homólogos electrónicos que resuelve varios problemas asociados con el proceso actual de reiniciado. Una ventaja es que el dispositivo copenazado recientemente desarrollado se puede fabricar utilizando equipos existentes en las fundiciones electrónicas tradicionales con un proceso de alineación pasiva menos costoso. Como resultado, la solución MIT promete ser rentable.

Un artículo sobre el dispositivo, que está patentado, apareció en la portada de Materiales de ingeniería avanzada a principios de este año. El otoño pasado, Drew Weninger, en el 57º Simposio Internacional sobre Microelectrónica. Weninger, un estudiante graduado en el Departamento de Ciencia e Ingeniería de Materiales (DMSE), ganó el premio al mejor artículo de estudiantes en el evento.

Además de Weninger, Kimerling y Agarwal, los autores del periódico son Samuel Serna de la Universidad Estatal de Bridgewater y Luigi Ranno, un estudiante graduado de DMSE.

Hacia una industria de microchip de eficiencia de recursos

Considere lo siguiente: en 2020, el número de teléfonos celulares, unidades GPS y otros dispositivos conectados a la “nube”, o grandes centros de datos superará los 50 millones, según Kimerling. Y el tráfico de centros de datos, a su vez, se está ampliando 1,000 veces cada 10 años.

Esta comunicación consume energía. Y “Todo tiene que suceder a un costo constante de energía, porque el producto interno bruto no está cambiando a ese ritmo”, dice Kimerling, quien también está afiliado a la MRL. La solución es producir más energía o hacer que la tecnología de la información sea más eficiente energéticamente.

Imágenes que detallan el proceso de fabricación. En a), el flujo de proceso utilizado para fabricar y empaquetar los prototipos de acoplamiento de chip a chip. En B), las imágenes SEM de sección transversal muestran los tamaños de características mínimas y máximas para el SOI y el SIN 𝑥. En C, D), el prototipo de chip a chip y el chip de vidrio separado en la etapa de prueba. En E), un esquema de la configuración de la prueba. Crédito: Materiales de ingeniería avanzada (2024). Doi: 10.1002/adem.202402095

La integración de la fotónica con la electrónica que sustenta los microchips de hoy en día podría abordar este último porque la transmisión o la comunicación de los datos que usan la luz es mucho más eficiente energéticamente. “Nuestro mantra es usar electrónica para la computación y la fotónica para la comunicación para controlar esta crisis energética”, dice Agarwal.

Sin embargo, esta solución viene con sus propios desafíos.

Por ejemplo, actualmente es difícil y costoso conectar chips electrónicos con sus contrapartes fotónicas dentro de un solo paquete. Esto se debe a que la fibra óptica, que tiene un diámetro central de diez micrómetros (diez millones de un metro), y el chip fotónico, que tiene dimensiones transversales de solo dos décimas por cinco décimas de un micrómetro, debe alinearse casi perfectamente o la luz se dispersará. Como resultado, hoy cada conexión debe probarse activamente con un láser para garantizar que la luz aparezca.

“Y el número de fibras que necesitaremos para una mayor comunicación de datos está aumentando exponencialmente, por lo que este proceso de alineación activa no lo reducirá para escalar hacia adelante”, dijo Weninger.

Más margen de maniobra

El nuevo dispositivo, llamado acoplador evanescente, ofrece mucho más margen de maniobra para conectar las fibras dentro del paquete electrónico-fotónico. “Los acopladores convencionales tienen un solo punto de acoplamiento, lo que hace que las tolerancias de alineación sean muy apretadas. Pero nuestro nuevo acoplador tiene una longitud de interacción mucho mayor que aumenta la tolerancia de la alineación”, dice Agarwal. Como resultado, los robots podrían ensamblar pasivamente los circuitos integrados resultantes que permiten pasar más luz sin perderse (no se necesita una alineación de láser activo).

Otra innovación clave: el acoplador “nos permite transmitir luz verticalmente” entre las múltiples capas de chips que comprenden el todo, dice Ranno. Eso en sí mismo es una hazaña importante porque es difícil dirigir la luz desde un plano horizontal.

“En electrónica es muy simple. Los electrones pueden fluir fácilmente fuera del plano”, dice Weninger. En contraste, “la luz nunca quiere tomar ángulos rectos”. El nuevo acoplador permite que la luz realice el salto entre las chips apilados.

Ranno concluye: “Hemos desarrollado un diseño de empaque (para integrar la fotónica con la electrónica) que es confiable, tiene una mayor tolerancia de alineación, no pierde mucha luz y no pierde demasiado espacio. Básicamente, tiene todas las características que desea para una interconexión eficiente y funcional”.

Este trabajo se llevó a cabo en parte a través del uso de instalaciones en MIT.Nano, e incluye contribuciones del consorcio de envasado electrónico-fotónico del MIT.

Más información: Drew Weninger et al, acopladores de baja pérdida de chip a chip para ópticas de alta densidad empaquetadas, materiales avanzados de ingeniería (2024). Dos: 10.1002/adem.202402095

Proporcionado por Materials Research Laboratory, Instituto de Tecnología de Massachusetts

Esta historia se vuelve a publicar por cortesía de MIT News (web.mit.edu/newsoffice/), un sitio popular que cubre noticias sobre la investigación del MIT, la innovación y la enseñanza.

Cita: Método rentable desarrollado para un paquete de chips fotónicos y electrónicos (2025, 28 de julio) Recuperado el 28 de julio de 2025 de https://techxplore.com/news/2025-07-efective-method-potonic-electronic-chips.html

Este documento está sujeto a derechos de autor. Además de cualquier trato justo con el propósito de estudio o investigación privada, no se puede reproducir ninguna parte sin el permiso por escrito. El contenido se proporciona solo para fines de información.